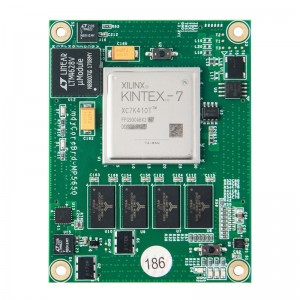

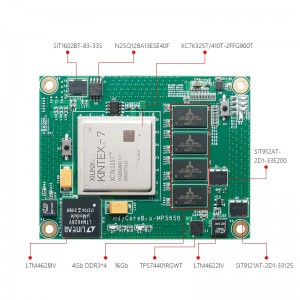

FPGA XILINX-K7 KINTEX7 XC7K325 410T vasega Alamanuia

DDR3 SDRAMQ: 16GB DDR3, 4GB i le fasi pepa, 16bit Data Bit Data Bid SPI Flash: Tasi le fasi 128MBITQSPIFLASH, lea e mafai ona faʻaaogaina mo faila faʻatulagaina FPGA ma le teuina o faʻamatalaga faʻamatalaga FPGA Bank tulaga faʻafesoʻotaʻi: fetuutuunai 1.8V, 2.5V, 3.3V eletise Afai e te manaʻomia le sui o le tulaga eletise pe a manaʻomia le sui o le tulaga maneta. fetuutuunaiga. Autu laupapa sapalai malosiaga: 5V-12V laina o le sapalai eletise EEPROM; M24C02-WMN6TP e fa'avae ile masini pasi I2C. Mulimuli i le auala amata o le laupapa autu o le laina lona lua protocols: lagolagoina e lua auala amata, o le JTAG, QSPI Flash connectors. Taulaga faalautele, 120pin, Panasonic AXK5A2137yg MP5700 ipu pito i lalo SFP interface: 2 modules opitika e mafai ona ausia maualuga-saosaoa fiber opitika fesootaiga, e pei o le maualuga 6GB/s lalo uati ipu: 1 200MHz faasinoupu uati fesootai i le laupapa autu MRCC uati tube vae, 1 125MHz le ipu uati faagaau pito i lalo o le GTXpin uati pito i lalo. uafu: faasao se 2.54mm tulaga faataatitia va 40 -shot faalautele taulaga, lea e faaaoga e fesootai le tagata faatau lava mamanu module. Essence Core uati laupapa: e tele fa'apogai uati i luga o le laupapa. E aofia ai le 200MHz system clock, le 125MHz GTX clock, ma le 66MHz EMCCLK clock. Taulaga JTAG: 10 stitches 2.54mm tulaga JTAG taulaga, mo le downloading ma debugging LEDs mo polokalame FPGA: o le aofaiga atoa o 6 mumu moli moli i totonu o le laupapa autu, e faailoa ai le tuuina atu o le mana o le pepa laupapa, 4 faailo faailoilo moli ma FPGA IO tube vae fesootai tuusao Key: 4 ki. 4 ki. O latou FPGA reset buttons, Program_b ki ma lua fa'aoga ki.

O le FPGA Xilinx-K7 Kintex7 XC7K325 410T o se faʻataʻitaʻiga faʻapitoa o le FPGA (Field-Programmable Gate Array) na atiaʻe e Xilinx. O nisi nei o fa'amatalaga autu e uiga i lenei FPGA: Fa'asologa: Kintex-7: Xilinx's Kintex-7 series FPGAs ua mamanuina mo talosaga maualuga ma ofoina atu se paleni lelei i le va o le faatinoga, malosi, ma le tau.Measini: XC7K325: E faasino lea i le masini faapitoa i totonu o le Kintex-7 faasologa. O le XC7K325 o se tasi o fesuiaiga o loʻo maua i lenei faʻasologa, ma e ofoina atu ni faʻamatalaga patino, e aofia ai le gafatia o le cell logic, fasi DSP, ma le I / O count.Logic Capacity: O le XC7K325 o loʻo i ai le gafatia o le cell logic o 325,000. O sela fa'akomepiuta o poloka faufale e mafai ona fa'apolokalameina i totonu o se FPGA e mafai ona fa'atulagaina e fa'atino ai ta'aloga numera ma galuega. O le numera saʻo o fasi pepa DSP i le XC7K325 e mafai ona fesuisuiaʻi e faʻatatau i le eseesega. O nei pine e mafai ona faʻaogaina e faʻafesoʻotaʻi ma masini i fafo poʻo isi masini numera. O isi mea: O le XC7K325 FPGA e mafai ona i ai isi vaega, e pei o poloka manatua faʻapipiʻi (BRAM), transceivers maualuga-saoasaoa mo fesoʻotaʻiga faʻamatalaga, ma filifiliga faʻatulagaina eseese. E taua le maitauina o FPGA e pei o le Xilinx-K7 Kintex7 XC7K325 e mafai ai ona e faʻaogaina polokalame faʻainitaneti ma faʻaogaina masini e mafai ona faʻaogaina. sela. O lenei fetuutuunai e mafai ai ona talafeagai mo le tele o faʻaoga, e aofia ai le faʻaogaina o komipiuta maualuga, faʻasologa o faʻailoga numera, ma le faʻavaveina o meafaigaluega.

Vaega o oloa

-

Telefoni

-

I-meli

-

Whatsapp

-

Skype

-

Skype

-

Skype