Tasi-stop Electronic Manufacturing Services, fesoasoani ia te oe e faigofie ona ausia au oloa faaeletonika mai PCB & PCBA

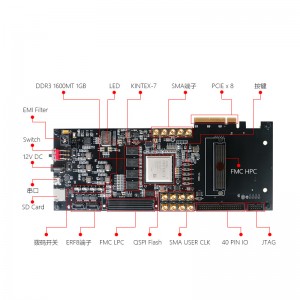

FPGA Xilinx K7 Kintex7 PCIe feso'ota'iga fiber opitika

- DDR3 SDRAM: 16GB DDR3 64bit pasi, fa'amaumauga 1600Mbps

- QSPI Flash: O se fasi 128mbit QSPIFLASH, lea e mafai ona faʻaogaina mo faila faʻatulagaina FPGA ma faʻamaumauga faʻamaumauga a tagata.

- PCLEX8 fa'aoga: O le fa'aoga masani a le PCLEX8 e fa'aoga e feso'ota'i ai ma le feso'ota'iga PCIE o le fa'ailoga komipiuta. E lagolagoina le PCI, Express 2.0 tulaga. Ole fua ole feso'otaiga e tasi e mafai ona maualuga ile 5Gbps

- USB UART uafu serial: O se laina telefoni, fesootai i le PC e ala i le miniusb uaea e faatino fesootaiga faasologa

- Micro SD card: Microsd card seat i le auala atoa, e mafai ona e faʻafesoʻotaʻi le Microsd card masani

- Temperature sensor: o le vevela vevela puʻe LM75, lea e mafai ona mataʻituina le vevela o le siosiomaga i luga o le laupapa atinaʻe

- FMC fa'alautele uafu: o le FMC HPC ma le FMCLPC, lea e mafai ona fetaui ma pepa fa'alautele tulaga fa'alautele.

- ERF8 maualuga-saosaoa feso'ota'iga terminal: 2 ERF8 ports, lea e lagolagoina ultra-maualuga-saosaoa fa'asalalauga fa'aliga fa'aopoopo 40pin: fa'aagaga se fa'aopoopoga lautele IO fa'aoga ma le 2.54mm40pin, aoga O e 17 paga, lagolago 3.3V

- O le fesoʻotaʻiga lautele o le maualuga ma le 5V tulaga e mafai ona faʻafesoʻotaʻi faʻasalalauga lautele o fesoʻotaʻiga 1O faʻapitoa lautele.

- SMA terminal; 13 maualuga maualuga auro - faʻapipiʻiina ulu SMA, lea e faigofie mo tagata faʻaoga e galulue faʻatasi ma le televave AD / DA FMC faʻalauteleina kata mo le aoina ma le gaosiga o faailo.

- Puleaina o le Uati: Fa'atele-uati puna. E aofia ai le 200MHz system differential clock source SIT9102

- Osilasi tioata eseese: 50MHz tioata ma le SI5338P polokalame fa'atonutonu uati pu: fa'apipi'iina i

- 66MHz EMCCLK. E mafai ona fetuutuuna'i sa'o ile fa'aoga eseese ole taimi ole uati

- JTAG taulaga: 10 su'isu'i 2.54mm tulaga JTAG taulaga, mo download ma debugging o polokalame FPGA

- Sub-reset voltage mata'ituina pu: o se vaega o le ADM706R voltage mata'ituina pu, ma le faamau ma le faamau e maua ai se faailoilo toe setiina lalolagi mo le faiga.

- LED: 11 moli moli, fa'aalia le sapalai eletise o le pepa laupapa, fa'ailoga config_done, FMC

- Fa'ailoga fa'ailo malosi, ma le 4 fa'aoga LED

- Ki ma ki: 6 ki ma 4 ki o FPGA toe seti faamau,

- Polokalama B fa'amau ma 4 fa'aoga ki o lo'o fatuina. 4 tasi -ifi togi lua ki

Tusi lau savali iinei ma lafo mai ia i matou

Vaega o oloa

-

Telefoni

-

I-meli

-

Whatsapp

-

Skype

-

Skype

-

Skype